abc Asembler - elektronski priručnik

I dio Uvod u Asembler

Adresiranje podataka u memoriji

Proces preko kojeg procesor kontroliše izvršavanje instrukcija je poznat kao fetch-decode-execute ciklus ili ciklus izvršavanja. On se sastoji od 3 uzastopna koraka:

- Dohvatanje instrukcije iz memorije (fetch)

- Dekodiranje ili identifikovanje instrukcije (decode)

- Izvršavanje instrukcije (execute)

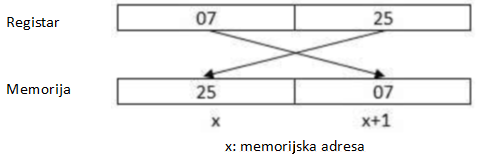

Procesor može pristupiti jednom ili više bajtova memorije u isto vrijeme. Posmatrajmo heksadecimalni broj 0725H (slovo H na kraju označava da se radi o heksadecimalnom broju). Ovaj broj će zahtijevati 2 bajta memorije. Bajt višeg reda ili najznačajniji bajt je 07, a bajt nižeg reda je 25.

Procesor sprema podatke u sekvenci obrnutih bajtova, tj. bajt nižeg reda je

spremljen u nižu memorijsku adresu, a bajt višeg reda u višu memorijsku adresu.

Dakle, ako procesor donosi vrijednost 0725H iz registra u memoriju, prvo će

prenijeti 25 u nižu memorijsku adresu, a 07 u sljedeću memorijsku adresu.

Kada procesor dobija numerički podatak iz memorije u registar, on ponovo vrši obrtanje bajtova. Postoje dve vrste memorijskih adresa:

- Apsolutna adresa – direktna referenca određene lokacije.

- Segmentna adresa (ili offset) – početna adresa memorijskog segmenta sa offset vrijednošću.

Binarnaaritmetika < Index > Radno okruženje

|

|

|

|

|

|

|